Fault model

A fault model is an engineering model of something that could go wrong in the construction or operation of a piece of equipment. From the model, the designer or user can then predict the consequences of this particular fault. Fault models can be used in almost all branches of engineering.

Basic fault models

Basic fault models in digital circuits include:

- the stuck-at fault model. A signal, or gate output, is stuck at a 0 or 1 value, independent of the inputs to the circuit.

- the bridging fault model. Two signals are connected together when they should not be. Depending on the logic circuitry employed, this may result in a wired-OR or wired-AND logic function. Since there are O(n^2) potential bridging faults, they are normally restricted to signals that are physically adjacent in the design.

- the transistor faults. This model is used to describe faults for CMOS logic gates. At transistor level, a transistor maybe stuck-short or stuck-open. In stuck-short, a transistor behaves as it is always conducts (or stuck-on), and stuck-open is when a transistor never conducts current (or stuck-off). Stuck-short will produce a short between VDD and VSS.

- The open fault model. Here a wire is assumed broken, and one or more inputs are disconnected from the output that should drive them. As with bridging faults, the resulting behavior depends on the circuit implementation.

- The delay fault model, where the signal eventually assumes the correct value, but more slowly (or rarely, more quickly) than normal.

Fault assumption

A fault model, falls under one of the following assumptions:

- single fault assumption: only one fault occur in a circuit. if we define k possible fault types in our fault model the circuit has n signal lines, by single fault assumption, the total number of single faults is k×n.

- multiple fault assumption: multiple faults may occur in a circuit.

Fault collapsing

There are two main ways for collapsing fault sets into smaller sets.

Equivalence collapsing

It is possible that Two or more faults, produce same faulty behavior for all input patterns. these faults are called equivalent faults. Any single fault from the set of equivalent faults can represent the whole set. In this case, much less than k×n fault tests are required for a circuit with n signal line. removing equivalent faults from entire set of faults is called fault collapsing. fault collapsing significantly decreases the number of faults to check.

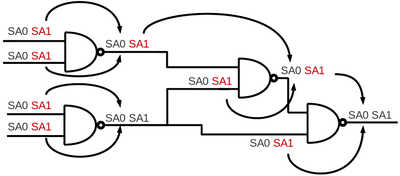

In the example diagram, red faults are equivalent to the faults that being pointed to with the arrows, so those red faults can be removed from the circuit. In this case, the fault collapse ratio is 12/20.

Dominance collapsing

Fault F is called dominant to F' if all tests of F' detects F. In this case, F can be removed from the fault list. If F dominates F' and F' dominates F, then these two faults are equivalent.[1]

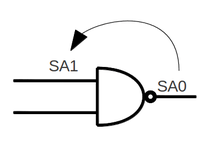

In the example, a NAND gate has been shown, the set of all input values that can test output's SA0 is {00,01,10}. the set of all input values that can check first input's SA1 is {01}. In this case, output SA0 fault is dominant and can be removed from fault list.

Functional collapsing

Two faults are functionally equivalent if they produce identical faulty functions[2] or we can say, two faults are functionally equivalent if we can not distinguish them at primary outputs (PO) with any input test vector.[3]

fault model in an Aerospace context

A fault model in an Aerospace context is a set of structured information which helps users or systems to identify and isolate a problem that occurs on an engine, Line-replaceable unit (LRU), or Auxiliary power unit (APU) during a flight. Associated with this fault model may be a suggested repair procedure along with references to Aircraft maintenance manuals (~ Light maintenance manual ).

See also

References

- ↑ "Fault Modeling",[University of Michigan]

- ↑ "Using Hierarchy in Design Automation:The Fault Collapsing Problem ",[11th VLSI Design and Test Symposium Kolkata, August 8–11, 2007]

- ↑ Andreas Veneris, Robert Chang, Magdy S. Abadir, Sep Seyedi, "Functional Fault Equivalence and Diagnostic Test Generation in Combinational Logic Circuits Using Conventional ATPG"